SSD FPGA: Alternativa ao RAM Disk

O Que é um RAM Disk?

Um RAM Disk é uma área de armazenamento criada na memória RAM do sistema, tratada pelo sistema operacional como um dispositivo de armazenamento físico, similar a um disco rígido ou SSD. Sua característica principal é ser baseado em memória volátil, o que significa que os dados armazenados são perdidos quando o sistema é desligado ou reiniciado. Essa tecnologia oferece uma alternativa de armazenamento temporário extremamente rápida, ideal para situações que exigem acesso veloz a dados, mas sem a necessidade de persistência a longo prazo.

Vantagens e Desvantagens do RAM Disk

Vantagens

- Velocidade Superior: Acesso muito mais rápido comparado a dispositivos de armazenamento baseados em NAND flash ou SSDs tradicionais.

- Latência Mínima: Redução significativa na latência de leitura/escrita.

- Isolamento de Dados Temporários: Ideal para armazenar dados temporários que não precisam de persistência após o desligamento.

Desvantagens

- Volatilidade: Perda de dados em caso de desligamento ou falha de energia.

- Consumo de Memória: Utiliza a RAM do sistema, que é um recurso limitado.

Consumo de Memória e Soluções Alternativas

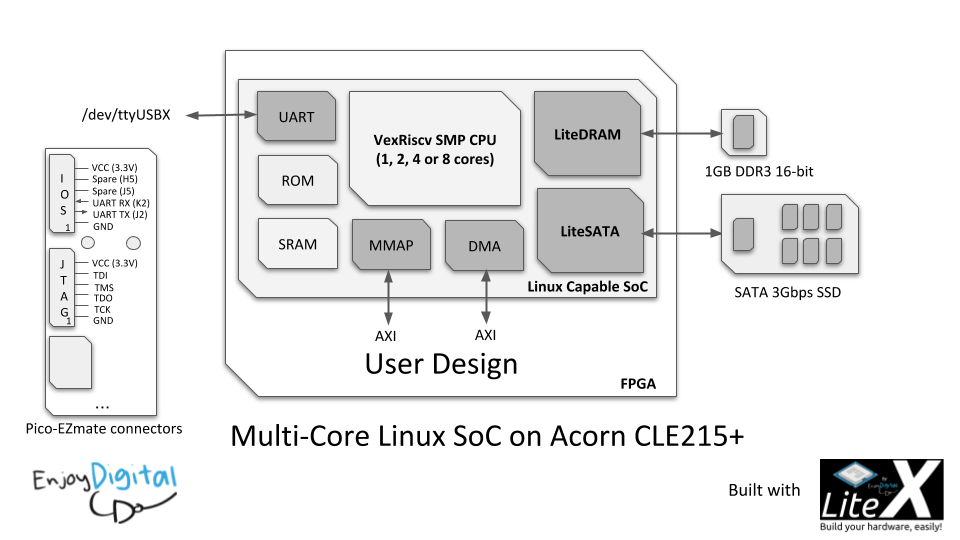

Uma abordagem inovadora para lidar com o consumo de memória do sistema é a implementação de um SSD SATA em FPGA utilizando LiteSATA e LiteDRAM como backend de memória. Este método requer a seleção de uma placa FPGA apropriada com recursos necessários, incluindo transceptores capazes de operar na velocidade SATA desejada e memória DRAM compatível. O processo envolve a configuração do LiteDRAM e LiteSATA, implementação de lógica de controle, integração dos componentes, compilação e síntese do design, e programação do FPGA. Esta solução oferece uma alternativa flexível e personalizável para o armazenamento de alta velocidade.

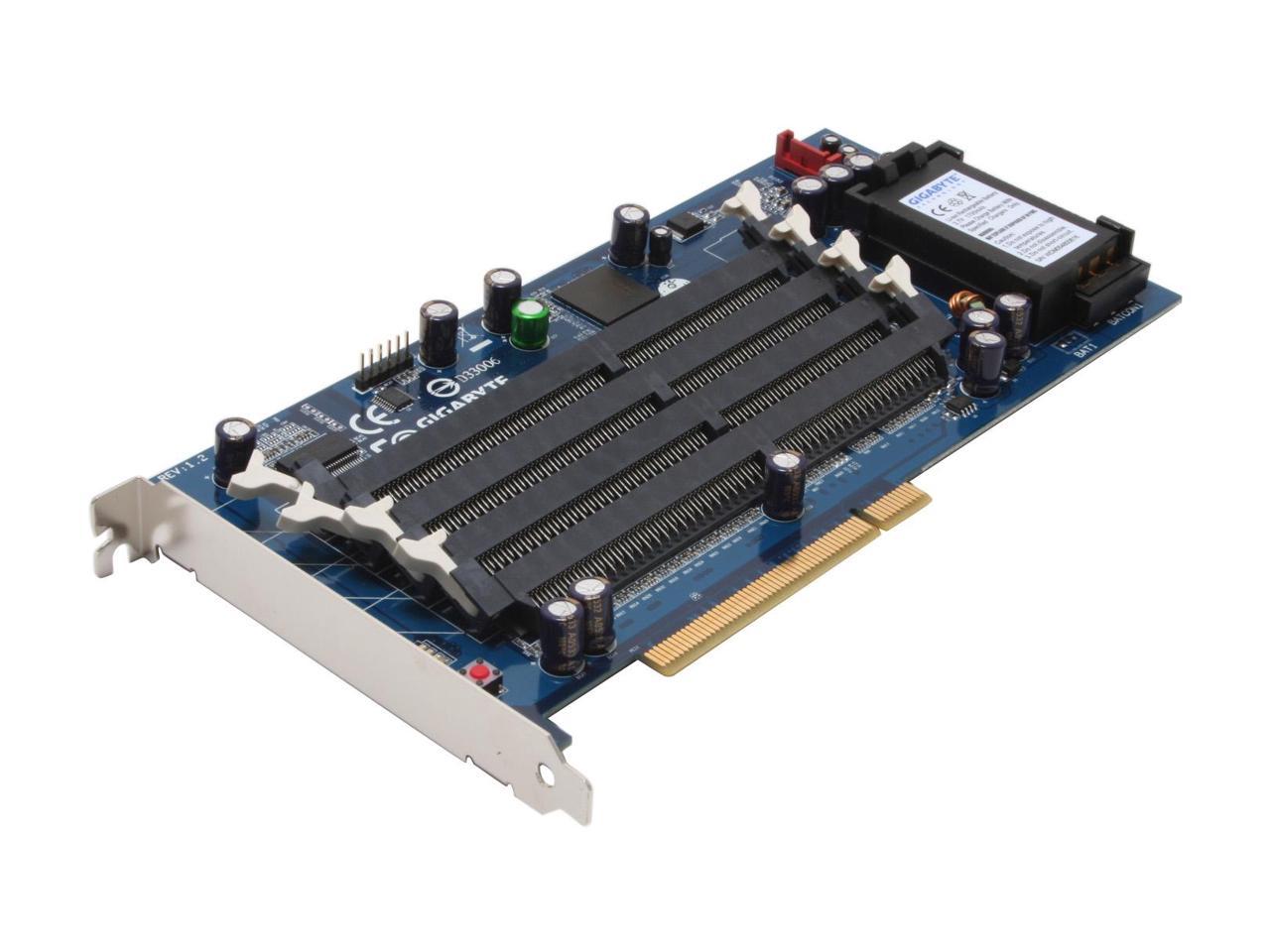

1. Seleção da Placa FPGA

Escolha uma placa com transceptores adequados e memória DRAM compatível.

2. Configuração do LiteDRAM e LiteSATA

Instancie e configure os núcleos LiteDRAM e LiteSATA no design FPGA.

3. Implementação da Lógica de Controle

Desenvolva um controlador para interfacear LiteSATA com LiteDRAM.

4. Programação e Teste

Compile, sintetize e programe o FPGA, seguido por testes e otimizações.

Configuração do LiteDRAM

1. Instanciação

No seu design, instancie o núcleo LiteDRAM.

2. Configuração

Configure o LiteDRAM para corresponder ao tipo e à configuração da memória DRAM na sua placa (por exemplo, DDR3, DDR4).

3. Parâmetros

Defina parâmetros como frequência de operação, largura de banda e latências.

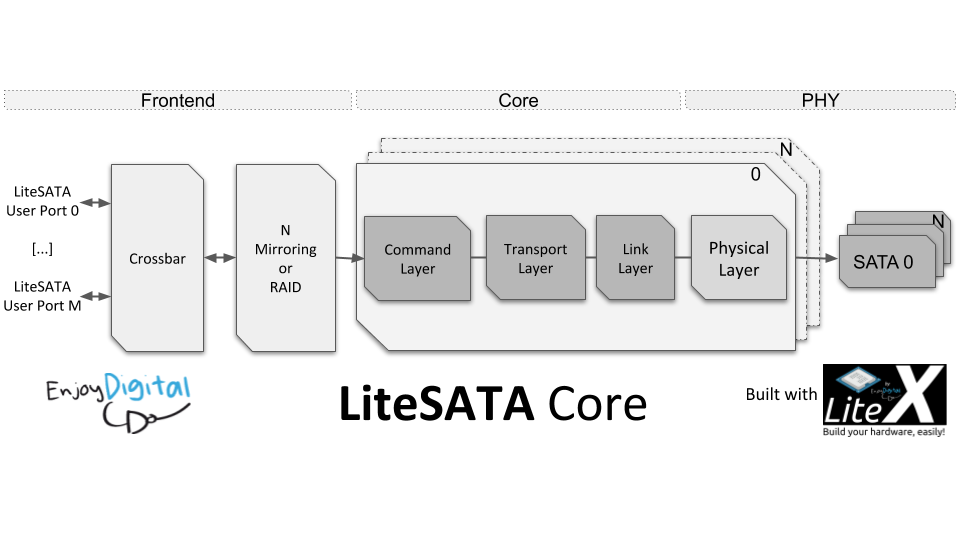

Configuração do LiteSATA

Instanciação

Comece por instanciar o núcleo LiteSATA no seu design FPGA.

PHY SATA

Em seguida, configure o PHY SATA de acordo com o hardware da sua placa FPGA, incluindo a taxa de transferência desejada. Por exemplo, para uma conexão SATA 3.0, a taxa de transferência será de 6 Gbps.

Mapeamento de Pinos

Por fim, certifique-se de que os pinos do FPGA estão corretamente mapeados para os conectores SATA.

Desenvolvimento do Controlador com Máquina de Estados Finitos

O desenvolvimento de um controlador que interfaceia o LiteSATA com o LiteDRAM utilizando uma Máquina de Estados Finitos (FSM) é crucial para gerenciar a comunicação entre o protocolo SATA e a memória DRAM. Este controlador é responsável por receber e interpretar comandos SATA, gerenciar operações de leitura/escrita na DRAM, e sincronizar dados entre os sistemas. A FSM é composta por vários estados, cada um representando uma etapa específica do processamento. A transição entre estados é baseada em eventos ou condições, como a recepção de um novo comando ou a conclusão de uma operação de leitura/escrita.

Objetivo do Controlador

Gerenciar comunicação entre SATA e DRAM, traduzindo comandos e garantindo integridade dos dados.

Estrutura da FSM

Estados representam etapas do processamento, com transições baseadas em eventos ou condições.

Implementação

Desenvolvimento de lógica para cada estado, garantindo fluxo correto de operações e tratamento de erros.

Estados da Máquina de Estados Finitos

A Máquina de Estados Finitos (FSM) do controlador é composta por vários estados essenciais. O estado IDLE é o ponto inicial, aguardando comandos. O COMMAND_DECODE decodifica os comandos recebidos. READ_SETUP e WRITE_SETUP preparam as operações de leitura e escrita, respectivamente. READ_EXECUTE e WRITE_EXECUTE realizam as operações de leitura e escrita na DRAM. O STATUS_UPDATE atualiza o status da operação e informa o host. O ERROR_HANDLE lida com erros ocorridos durante as operações. Cada estado tem ações específicas e critérios de transição para outros estados, garantindo um fluxo de operação eficiente e confiável.

- IDLE: Aguarda comandos, transição para COMMAND_DECODE ao receber novo comando.

- COMMAND_DECODE: Decodifica o comando recebido e prepara parâmetros.

- READ/WRITE_SETUP: Configura operações de leitura ou escrita na DRAM.

- READ/WRITE_EXECUTE: Executa operações de leitura ou escrita na DRAM.

- STATUS_UPDATE: Atualiza o status da operação e informa o host.

Comparação entre RAM Disk e SSD SATA em FPGA

RAM Disk e SSD SATA em FPGA com LiteSATA e LiteDRAM compartilham semelhanças em termos de velocidade superior e uso de memória volátil. Ambos oferecem velocidades de leitura/escrita superiores aos dispositivos de armazenamento convencionais. No entanto, diferem significativamente em sua implementação de hardware e flexibilidade. O RAM Disk é uma solução puramente de software que utiliza a RAM interna do sistema, enquanto o SSD em FPGA envolve hardware personalizado conectado a DRAM externa. A escalabilidade e flexibilidade também diferem, com o SSD em FPGA oferecendo maior potencial de expansão.

| Característica | RAM Disk | SSD SATA em FPGA |

|---|---|---|

| Implementação | Software | Hardware personalizado |

| Escalabilidade | Limitada pela RAM do sistema | Expansível com módulos DRAM |

| Flexibilidade | Baixa | Alta (ajustável via FPGA) |

| Persistência | Volátil | Volátil (com opções de backup) |

Integração com a Partição de Swap no Linux

A integração de um SSD SATA em FPGA com a partição de swap no Linux pode acelerar significativamente o desempenho do sistema. O Linux utiliza o swap como uma extensão da memória RAM, e um swap mais rápido permite que o sistema mova páginas de memória para o swap e as recupere mais rapidamente, aumentando efetivamente o desempenho percebido da RAM. Essa integração resulta em redução do tempo de espera para processos que requerem acesso a dados no swap, melhorando a eficiência geral do sistema. Em aplicações de alto desempenho, como bancos de dados, máquinas virtuais ou processamento de big data, um swap rápido pode evitar gargalos quando a memória física está esgotada.

1. Melhor Gestão de Memória

Movimento mais rápido de páginas entre RAM e swap, aumentando o desempenho percebido da memória.

2. Redução de Tempo de Espera

Processos acessam dados no swap mais rapidamente, melhorando a responsividade do sistema.

3. Melhoria em Aplicações de Alto Desempenho

Evita gargalos em workloads que exigem muita memória, como bancos de dados e processamento de big data.

Benefícios e Desvantagens da Integração

A integração de um SSD SATA em FPGA com LiteSATA e LiteDRAM como partição de swap no Linux oferece diversos benefícios. A latência reduzida e as altas taxas de transferência aceleram operações de leitura e escrita no swap. A ausência de desgaste por escrita na DRAM aumenta a longevidade do dispositivo. A capacidade pode ser expandida adicionando mais módulos DRAM, e atualizações são facilitadas via firmware. Contudo, existem desvantagens a considerar. A implementação requer hardware adicional (FPGA e DRAM externa), o que pode resultar em um custo mais elevado comparado a soluções de RAM Disk convencionais. A complexidade da implementação também pode ser um fator limitante para alguns usuários.

Benefícios

- Latência reduzida

- Altas taxas de transferência

- Ausência de desgaste por escrita

- Capacidade expansível

- Atualizações facilitadas

Desvantagens

- Necessidade de hardware adicional

- Potencial custo mais elevado

- Complexidade de implementação

Considerações Finais e Recursos

Compatibilidade de Protocolos

Garanta que o seu design esteja em conformidade com as especificações SATA para evitar problemas de compatibilidade.

Limitações de Hardware

Esteja ciente das limitações do seu FPGA, como recursos lógicos disponíveis e capacidades dos transceptores.

Segurança dos Dados

Considere implementar recursos de correção de erros ou proteção de dados se necessário.

Recursos Úteis:

- Repositório do LiteSATA:

https://github.com/enjoy-digital/litesata - Repositório do LiteDRAM:

https://github.com/enjoy-digital/litedram - Documentação do LiteX:

https://github.com/enjoy-digital/litex/wiki